In this lab exercise you will learn to implement binary adders. You will learn about the half-adder and the full-adder.

## LAB EXERCISE 6.1 Binary Adders Objectives

LD-2 Logic Designer

**Materials**

74LS86 Quad EXOR IC

74LS08 Quad AND IC

74LS32 QUAD OR IC

Jumper Wires

TTL Data Book

1. You will use a 74LS08 and a 74LS86 for the first part of this experiment. Place both of these ICs on the LD-2 breadboard and wire power to them.

**Procedure**

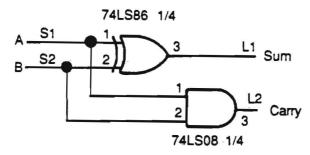

2. Wire the circuit shown in Figure 6-15.

FIGURE 6-15. Half-Adder Schematic.

- 3. Place S1 and S2 to their off positions. Turn on power. The power indicator, D1 should light.

- 4. Use S1 and S2 for the A and B inputs. Use L1 and L2 to observe the sum and carry outputs. Record the truth table for this circuit.

- 5. Turn off power.

- 6. Add a 74LS32 IC to the LD-2 breadboard. Wire power and ground to this circuit.

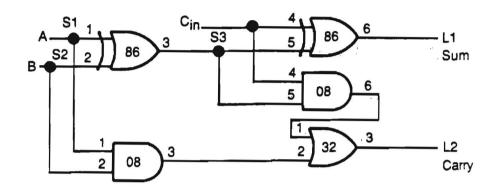

- 7. Wire the circuit shown in Figure 6-16.

FIGURE 6-16. Full-Adder Schematic.

- 8. Place S1, S2 and S3 to off. Turn on\_power. D1 should light.

- 9. Use S1, S2 and S3 for the A, B and Carry in inputs. Use L1 and L2 to observe the sum and carry outputs. Record your observations in the form of a truth table.

## Questions

1. Explain the difference between a half-adder and a full-adder.

2. Use the truth table from step 9 to form the logic equations and Karnaugh maps for the full-adder.

## LAB EXERCISE 6.2 Parallel Binary Adder

**Objectives**

In this lab exercise you will learn about the 4-bit parallel IC adder. You will use this adder to perform one's complement arithmetic.

LD-2 Logic Designer

**Materials**

7483 4-Bit Binary Full-Adder With Fast Carry

74LS86 Quad Two Input EXOR Gate

Jumper Wires

TTL Data Book

Ε

1. You will use the 74LS86, and 7483 ICs for this lab. Insert both of these ICs in the breadboard and wire the power and ground to both ICs. Be particularly careful with the 7483 as it has the power on pin 5 and ground on pin twelve of the 16 pin DIP.

Wire Augend

S4 = 11

**Procedure**

2. Wire the circuit shown in Figure 6-17.

S5 = 7 S6 = 4 S7 = 16

Augend

Augend

B 4 2 1

16 4 7 11 1 3 8 10

Cout

B4 B3 B2 B1 A4 A3 A2 A1 Cin

14 \( \Sigma 4 \)

S1 \( \Sigma 5 \)

L3 \( \L2 \)

L1 \( \L0 \)

T4LSB3

DS1

D FIGURE 6-17. Parallel Binary Adder Circuit.

3. This circuit requires some explanation. The four gates of the 74LS86 are used to form a true/complement circuit. This will allow you to add numbers with unlike signs.

74LSB6 4/4

|           | 4. | This circuit is connected so that the inputs act as unsigned magnitudes. Use S0-S3 as the A1-A4 inputs, S4-S7 as the B1- B4 inputs, L0-L3 as the sum output, and DS1 as the carry output. Observe this circuit and describe it's operation.                     |

|-----------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |    |                                                                                                                                                                                                                                                                 |

|           | 5. | Now you will configure this circuit for subtraction. Remove the wire connecting pins 2,5,9 and 13 of the 74LS86 to ground at the ground end.                                                                                                                    |

|           | 6. | Connect this wire to VCC. This will enable the complement output of the true/complement gate.                                                                                                                                                                   |

|           | 7. | Remove the jumper between pin 13 of the 7483 and ground. Connect this jumper wire to pins 13 and 14 of the 7483. This change will perform the end-around carry needed for one's complement arithmetic.                                                          |

|           | 8. | Place all logic switches to off. Turn on power and record your observations. Use the same inputs and outputs as step 5. Do not change the S4-S7 inputs at this time. Remember that the inputs on S0-S4 are entered into the adder in a one's complement format. |

|           | 9. | Use the S4-S7 switches as the input for the minuend while S0-S4 are used as the subtrahend. Describe the action of this circuit.                                                                                                                                |

|           |    |                                                                                                                                                                                                                                                                 |

| Questions | 1. | Describe the two different types of adders used in this laboratory.                                                                                                                                                                                             |

- 2. Show two ways that the 7483 can represent a 0 when connected as a one's complement subtractor.

- 3. What changes would have to be made for the circuit of step 8 in order for the circuit to add two positive binary numbers?

In this lab exercise you will learn about the BCD adder. You will construct a BCD adder and observe it's operation.

LAB EXERCISE 6.3 The BCD Adder

Objectives

LD-2 Logic Designer

**Materials**

7483 4-Bit Adder (2)

74LS27 Triple Three Input NOR

74LS04 Hex Inverter

74LS08 Quad AND

Jumper Wires

TTL Data Book

- 1. Place two 7483s, a 74LS08, a 74LS27, and a 74LS04 on the breadboard and wire power and ground to them.

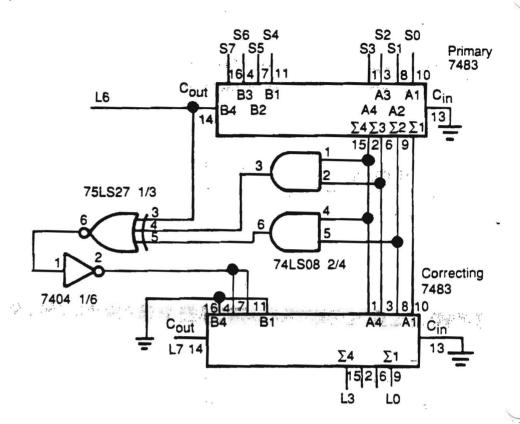

- 2. Wire the circuit shown in Figure 6-18.

FIGURE 6-18. BCD Adder Circuit.

- 3. Place all logic switches off. Turn-on power. Only D1 should light.

- 4. Use S0-S3 as one adder input and S4-S7 as the other adder input. L7 indicates a carry while L0-L4 indicate the sum output. Add several numbers and record your observations.

- 5. Turn off power. Remove the wires from L0-L3 and place them on DS2 A-DS2 D respectively. Wire DS1 DE and DS2 DE to +5 VDC. Remove the wires from L7 and L6 and place them on pins 1 and 2 of the 74LS27. Wire pin 13 of the 74LS27 to ground. Wire pin 12 of the 74LS27 to pin 3 of the 74LS04. Wire pin 4 of the 74LS04 to DS1 A.

- 6. Place all logic switches to off. Turn on power. Now use the same inputs as step 4 but this time use DS1 and DS2 as outputs. Again observe the adder operation and record your observations.

| the sum output for the circuit of s                | tep 6?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ques |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                                    | The state of the s | *    |

| What does the circuitry added 74LS27 in step 5 do? | to pins 1 and 2 of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 74L327 In step 3 do :                              | e for a set of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 74L327 Itt step 3 do :                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 74L327 It step 3 do :                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t.   |

In this lab exercise you will study the Arithmetic Logic Unit or ALU. You will use the ALU to perform binary multiplication and subtraction.

LAB EXERCISE 6.4

The ALU

Objectives

LD-2 Logic Designer

**Materials**

74181 Arithmetic Logic Unit

Jumper Wires

TTL Data Book

The 74181 ALU is the largest and most complex IC you have used to date. The 74181 performs a variety of arithmetic and logic functions on two four-bit inputs. It provides a four-bit with carry output. It has a carry input and is controlled by the S0-S4, and M inputs. The A and B inputs and the F output can be used as either true or complement bits. For this reason you will often find two function tables for the 74181 listed in data books.

**Procedure**

- 1. Place the 74181 on the breadboard and wire power and ground to it.

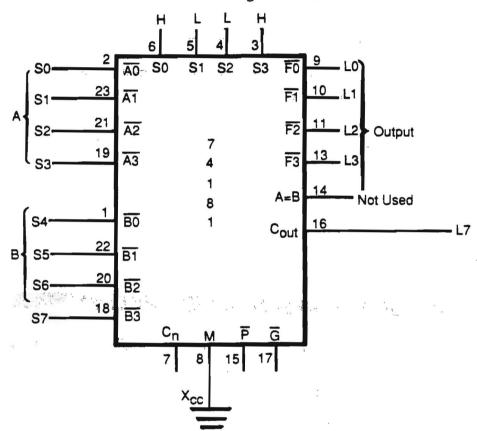

- 2. Wire the circuit shown in Figure 6-19.

FIGURE 6-19. 74181 Adder.

3. Place all logic switches to off. Turn on power. D1 and L7 should light. Use S0-S3 as the A input, S4-S7 as the B input, L0-L3 as the F output and L7 as the carry output. Observe and describe the action of this circuit. Remember that the carry output is LO true.

4. The 74181 can perform a variety of other functions. The type of function performed is controlled by the M input, while the function selection is via the S0-S4 inputs. Turn off power.

| pins 4 and           | g to pins 3-6. Wire pins 3 and 6 to 15 to VCC. Place all logic switches of                                 | ground and   |

|----------------------|------------------------------------------------------------------------------------------------------------|--------------|

| circuit's            | ame inputs and outputs as before. operation and describe it. Pa to incorrect arithmetic results.           |              |

|                      |                                                                                                            |              |

| power an<br>results. | power. Wire pin 7 to ground. 8 d observe the circuit's operation.  Again look for any incorrect operation. | Describe the |

| · · ·                |                                                                                                            |              |

|                      |                                                                                                            |              |